AI·HPC 시대에는 칩 자체만큼이나 어떻게 묶고 쌓느냐(첨단 패키징)가 성능·전력·비용을 좌우하는 핵심 변수가 되고 있다. TSMC가 2026년 Capex를 최대 560억달러까지 높이고 그 중 10~20%를 CoWoS 등 첨단 패키징·테스트·마스크에 투입하겠다고 밝힌 것도, 실제 병목이 공정보다 패키징·후공정에 생기고 있음을 보여준다.

목차

1. 첨단 패키징 개요

2. 첨단 패키징 발전 방향

3. 패키징 기술 트렌드

4. 첨단 패키징과 과제

5. 경쟁 구도와 지정학

6. 첨단 패키징 시장 규모와 테스트 수요

7. 주요 첨단 패키징 기업

1. 첨단 패키징 개요

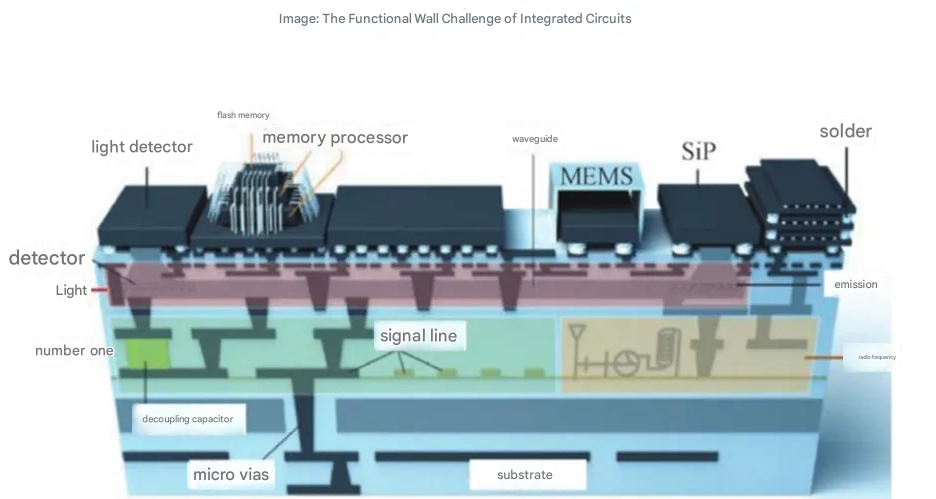

반도체 패키징은 칩을 보호하고 외부와 전기적으로 연결하며, 열을 빼내고 기판·모듈과 기계적으로 고정하는 공정이다. 전통 패키징은 ‘보호와 연결’이 목적이었다면, 첨단 패키징은 다수 칩을 더 촘촘하고 짧은 경로로 연결해 시스템 성능과 집적도를 끌어올리는 데 초점을 둔다.

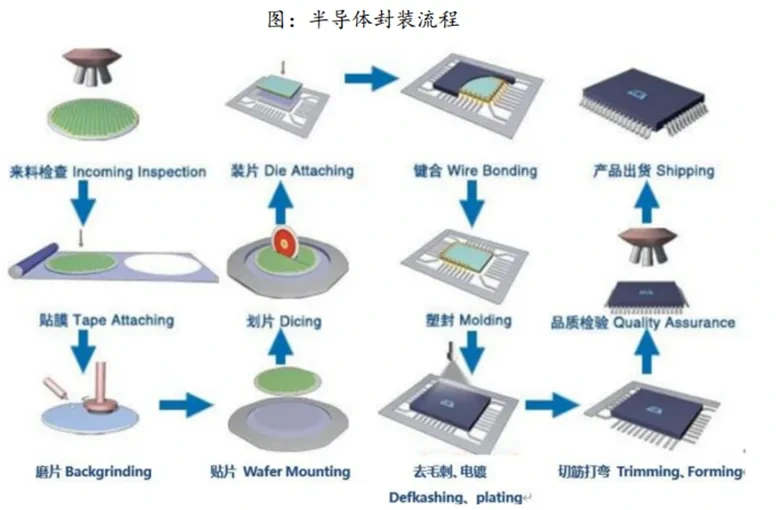

공정 단계는 웨이퍼 후면 연마·다이싱(절단)·다이 픽앤플레이스·본딩·몰딩·리드 성형·테스트 순으로 진행되며, 백엔드지만 CAPEX·기술 난도가 크게 올라가고 있다. 전통 패키징과 달리 첨단 패키징에서는 웨이퍼 레벨(WLP)에서 Bump·RDL·TSV 등 공정이 추가되며, 사실상 ‘제2의 제조 공정’ 역할을 한다

2. 첨단 패키징 발전 방향

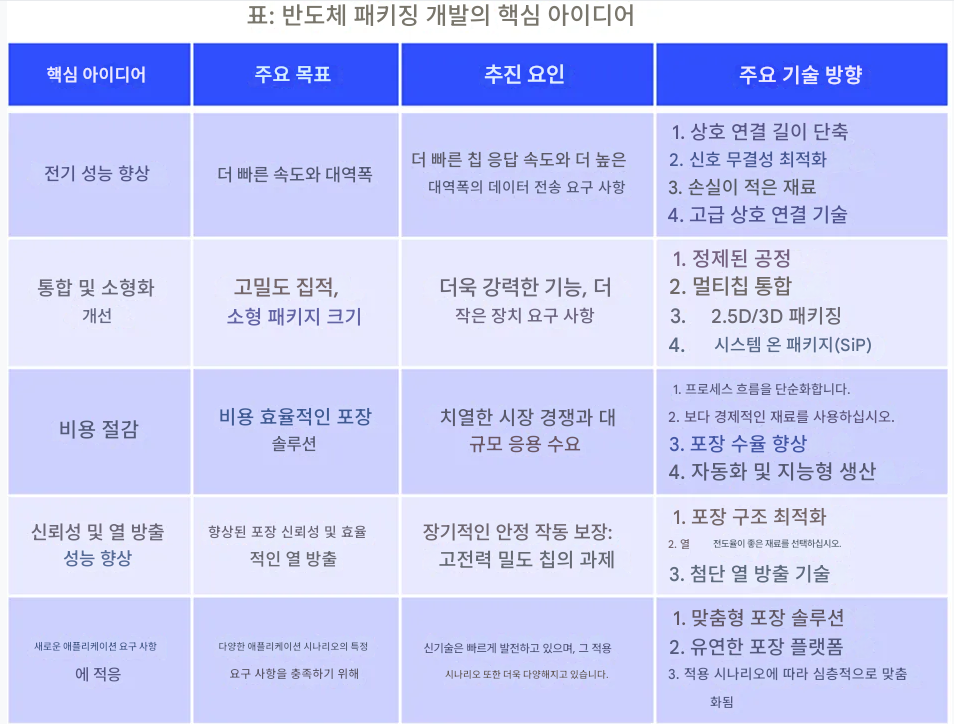

첨단 패키징의 핵심 특성은 고속 신호 전달, 다층·3D 적층, 높은 신뢰성과 낮은 코스트, 소형화, 안정적인 열 관리다. 이를 위해 패키징은 전기 성능 개선, 집적도·소형화 향상, 비용 절감, 신뢰성·방열 강화, 신규 응용(자동차·AI·5G)에 맞춘 형태로 진화해 왔다.

기술 단계로 보면, 통홀이 있는 DIP 등 THT(삽입형) → QFP·QFN 등 주변 리드형 SMT → BGA·CSP 등 배열 리드형 SMT → WLP·2.5D·3D·Chiplet 순으로 발전했다. 그 과정에서 Bump(미세 솔더볼), RDL(재배선), TSV(실리콘 관통전극), Wafer Level 패키징 기술이 첨단 패키징의 기반 모듈로 자리 잡았다.

3. 패키징 기술 트렌드

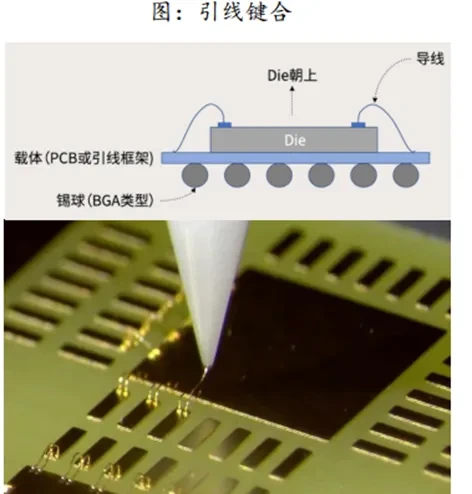

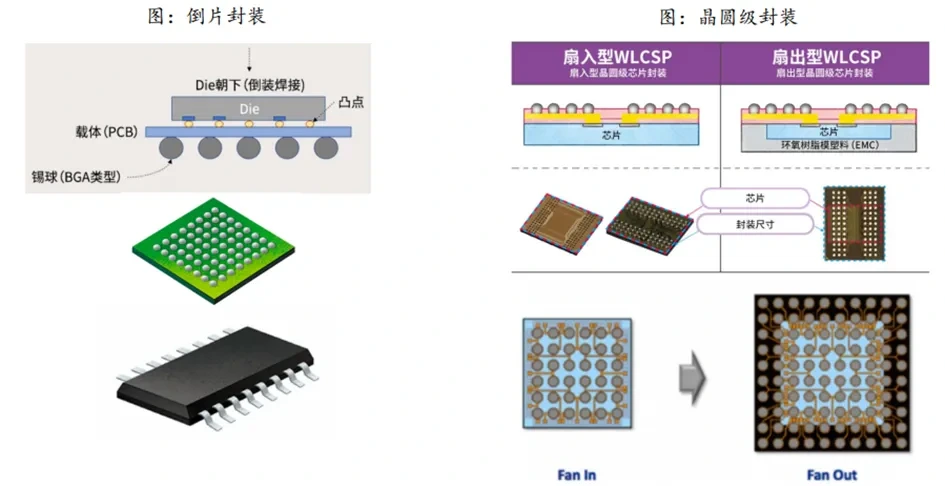

와이어 본딩은 금·알루미늄 와이어로 다이와 리드프레임을 연결하는 가장 전통적인 방식으로, 여전히 수량 기준으로는 다수를 차지한다. 반면 플립칩(Flip Chip)은 다이의 활성면을 아래로 향하게 한 뒤 Bump로 바로 기판에 붙이는 방식으로, 신호 경로가 짧아 고속·저전력에 유리해 GPU·네트워크 칩 등 고성능 제품의 기본 패키징이 되었다.

웨이퍼 레벨 패키징(WLP)은 웨이퍼 상태에서 패키징을 수행한 뒤 개별 칩으로 절단하는 방식이다. WLP 중 Fan-In은 칩 크기와 패키지 크기가 거의 같아 I/O 수가 제한적이고, Fan-Out(FOWLP)은 RDL을 통해 칩 밖 영역까지 I/O를 확장해 더 많은 핀을 구현한다.

2.5D 패키징(CoWoS, EMIB)은 실리콘 중간기판(인터포저)나 브리지 기판 위에 로직·HBM 등을 나란히 올려 고대역폭으로 연결하는 방식이다. 3D 패키징은 TSV를 활용해 칩을 수직으로 쌓는 구조로, 거리·지연·전력을 줄이는 대신 열·신뢰성 관리가 더 어려운 하이엔드 기술이다.

Chiplet은 여러 기능 블록을 하나의 SoC로 만들지 않고, 공정·IP별로 분리된 작은 칩(Chiplet)을 패키징 단계에서 묶어 하나의 시스템(SiP)로 만드는 개념이다. 동일한 정보량·속도를 유지하면서 대형 단일 다이 대비 수율·코스트·개발 유연성을 개선할 수 있어, 공정 고도화가 더뎌지는 후모어 시대에 가장 현실적인 해법으로 받아들여진다.

4. 첨단 패키징과 과제

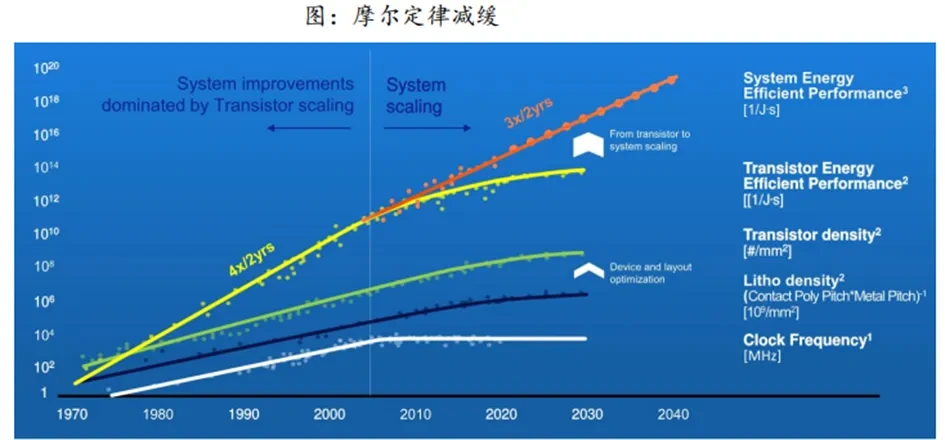

공정 미세화만으로 성능·비용을 개선하는 시대가 끝나가면서, ‘포스트 무어’ 시대의 핵심 전략은 이종 집적(heterogeneous integration)으로 이동했다. Chiplet·2.5D/3D 패키징은 서로 다른 공정·기능의 칩을 한 패키지 안에 묶어, 시스템 단위로 성능·전력·비용을 최적화한다.

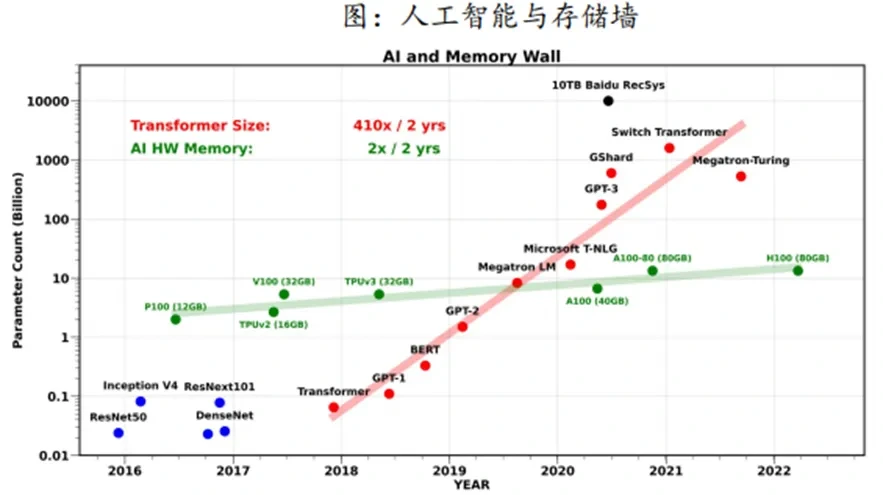

AI·HPC에서는 ‘메모리·인터커넥이 성능 병목’이 되는 메모리 월 문제가 본격화됐다. 지난 20년간 CPU 성능은 2년마다 3배씩 늘었지만 DRAM 대역폭은 1.6배, 인터커넥은 1.4배씩 늘어나는 수준에 그쳐, 패키징 레벨에서 계산과 메모리를 가깝게 붙여야 하는 필요가 커졌다.

HBM은 2.5D·3D 패키징을 통해 여러 층의 DRAM을 수직으로 쌓고, 인터포저를 통해 GPU·ASIC과 초고속으로 연결하는 구조다. 이렇게 하면 메모리 대역폭을 크게 늘리면서 메모리 월을 완화할 수 있고, CoWoS·EMIB·Chiplet과 결합해 AI 가속기 시스템 전체 효율을 끌어올릴 수 있다.

면적 월도 첨단 패키징이 푸는 과제다. EUV 노광기 한 번에 노출 가능한 최대 면적은 약 858㎟로 제한되는데, NVIDIA A100은 이미 826㎟ 수준까지 접근했다. 이보다 큰 단일 다이는 수율이 급락해(213㎟에서 59%→777㎟에서 26%) 경제성이 떨어지므로, 여러 중간 크기 다이를 2.5D/3D·Chiplet으로 묶는 방식이 필수적이 된다.

전력·열(파워 월)과 기능 복잡도(기능 월) 역시 패키징 단계에서 해결해야 할 과제다. 이종 집적은 기능별로 최적 공정을 선택해 전체 전력을 낮출 수 있고, 3D 전원 공급·고급 열 인터페이스 재료·전용 히트싱크 설계 등을 패키징 안에 녹여 전체 열 설계를 최적화한다. 동시에 SiP를 통해 디지털·아날로그·RF·전력·센서를 한 패키지에 담아, SoC 하나로는 구현하기 어려운 복합 기능을 시스템 단위로 구현할 수 있다.

5. 경쟁 구도와 지정학

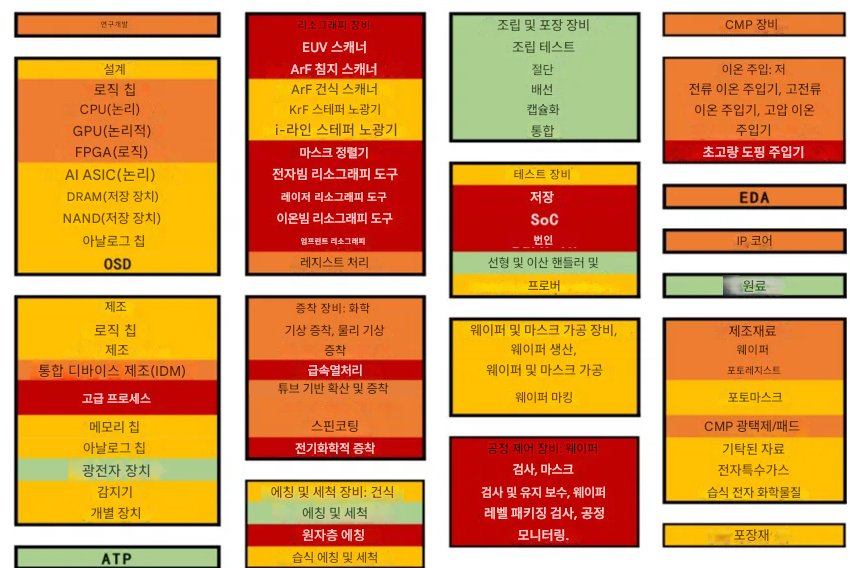

글로벌 패키징 매출 기준으로 대만이 43.7%로 압도적인 1위이며, 미국 21%, 중국 본토 20.2%가 뒤를 잇는다. 한국·말레이시아·싱가포르·일본도 의미 있는 비중을 차지하지만, 첨단 패키징의 중심축은 ‘대만 OSAT+TSMC, 미국 OSAT+IDM, 중국 전통 패키징’ 조합으로 볼 수 있다.

중국 본토는 아직 전통 패키징 위주다. 盛合晶微 자료에 따르면 2024년 중국 봉테 시장에서 첨단 패키징 비중은 15.5%에 불과해, 글로벌 평균 40%와 큰 격차가 있다. 그러나 TSMC CoWoS 캐파가 AI 서버 수요에 비해 빠듯한 상황, 중국 내 GPU·NPU 국산화 속도 등을 감안하면, 2024년 514억위안이던 중국 첨단 패키징 시장이 2029년 1,006억위안(CAGR 14.4%)까지 커질 것으로 예상된다.

정책 측면에서는 미국·중국이 모두 첨단 패키징을 전략 축으로 삼고 있다. 각국의 반도체 법·보조금 프로그램 안에는 패키징·테스트·OSAT 투자 인센티브가 포함되고, 이는 신규 라인·장비·인력 유치 경쟁으로 이어진다. 미국의 대중 규제는 주로 공정·장비·AI 칩에 초점이 맞춰져 있고, 패키징에는 상대적으로 직접 규제가 적어 중국 입장에서는 ‘뚫려 있는 고지’로 인식된다.

중국의 강점은 봉테·봉테 장비에서 이미 일정 수준의 국제 경쟁력을 갖추었다는 점이고, 약점은 EDA·IP·선단 재료·선단 장비 등 프런트엔드 전반이 여전히 ‘목을 죄는 지점’이라는 것이다. 결과적으로 첨단 패키징은 중국이 상대적으로 손을 쓸 수 있는 마지막 구간이자, 글로벌 AI·HPC 밸류체인에서 레버리지를 확보할 수 있는 지점이 된다.

6. 첨단 패키징 시장 규모와 테스트 수요

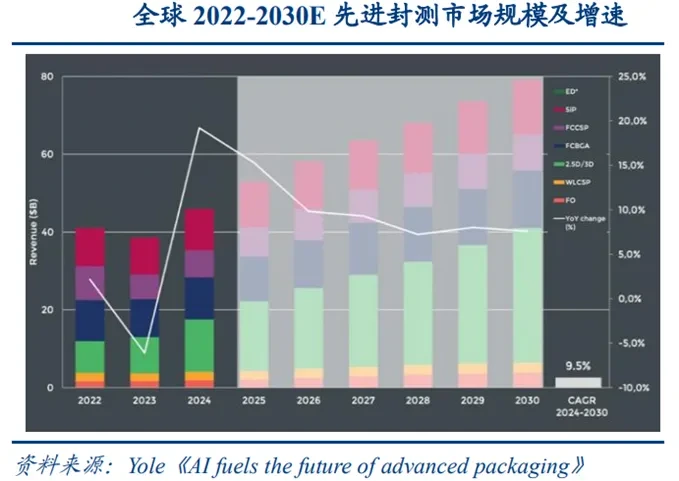

Yole·中商产业연구院에 따르면 2024년 글로벌 첨단 패키징 시장은 약 450억달러로, 전체 봉테 시장의 약 55%를 차지한다. AI·HPC·5G·자동차 전자 수요에 힘입어 2030년에는 약 800억달러까지 성장하고, 2024~2030년 CAGR은 9.4%로 전망된다.

Chiplet 구조 확산은 중간 테스트(KGD: Known Good Die)를 ‘필수 공정’으로 만든다. CoWoS 같은 2.5D 패키징에서는 하나의 모듈 안에 로직 다이·HBM 스택·실리콘 인터포저 등 고가 부품이 들어가고, 재작업이 거의 불가능하기 때문에 불량 다이가 들어가면 전체 모듈을 버려야 한다. 이 때문에 웨이퍼 테스트 외에 개별 다이에 대해 완제품 수준에 가까운 기능·신뢰성 테스트를 수행하는 KGD 공정이 추가되고, 고정밀 프로버·고급 테스터 수요가 구조적으로 늘어난다.

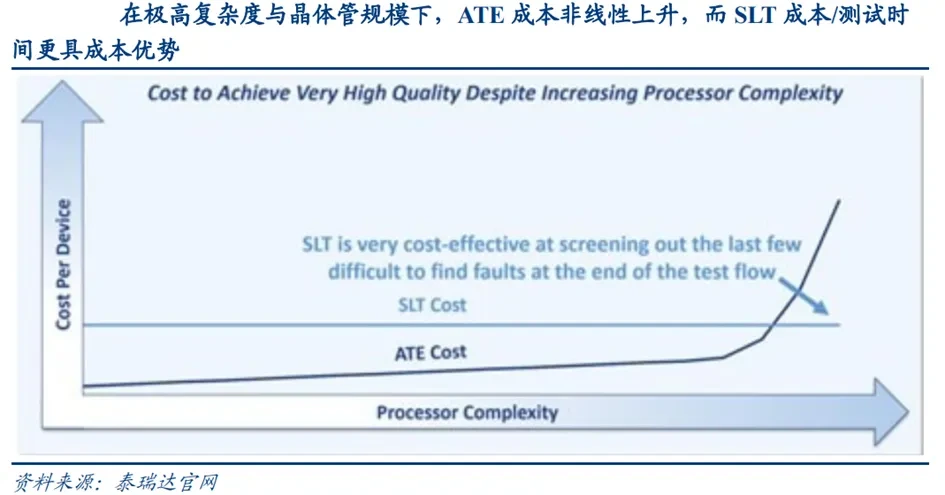

이종 집적·시스템 복잡도 상승은 시스템 레벨 테스트(SLT)를 ‘ATE 이후 두 번째 방화벽’으로 만든다. 기존 ATE는 구조화된 벡터를 써서 회로의 통전 여부를 확인하지만, AI/HPC 칩의 실제 사용 상황(소프트웨어·OS·메모리·인터커넥 연동)은 이런 테스트로는 다 걸러지지 않는다. SLT는 실제 OS·드라이버·애플리케이션을 띄운 상태에서 칩을 테스트해, 시스템 상호작용 문제를 잡아낸다. 현재 모든 주요 CPU·APU·GPU는 출하 전 SLT를 거치며, SLT 라인은 첨단 패키징 가치사슬에서 테스트 쪽 추가 CAPEX·OPEX를 의미한다.

7. 주요 첨단 패키징 기업

장전테크(长电科技,JCET)는 중국 최대 OSAT로, WLCSP·2.5D/3D·SiP·Flip Chip 등 풀 라인업을 갖춘 기업이다. 회사는 XDFOI®라는 Chiplet 지향 고밀도 Fan-Out 이종 집적 플랫폼을 양산 단계까지 끌어올렸고, HPC·AI·5G·자동차용 제품에 적용하고 있다. 고부가가치 비중이 늘면서 향후 마진·수익성 회복이 기대되는 구조다.

통푸마이크로(通富微电)는 메모리·자동차·HPC용 봉테 캐파 증설을 위해 44억위안 유상증자를 추진 중이다. 2025년 1~3분기 매출 201.2억위안(YoY +17.8%), 순이익 8.6억위안(YoY +55.7%)로 업계 상위 성장률을 기록했으며, AMD 등 글로벌 대형 고객 성장과 중국 스마트폰·자동차 국산화 수혜를 동시에 받고 있다.

화톈테크(华天科技)는 중국 상위 봉테사로, 2025년 1~3분기 순이익이 51.98% 증가했다. ePoP/PoP 메모리, 자동차용 FC-BGA, 2.5D/3D 라인, CPO 패키징, FOPLP 등 첨단 패키징 기술을 개발·양산하며, 난징에 2.5D/3D 첨단 패키징 JV(자본금 20억위안)를 설립해 규모 확대를 노리고 있다.

융시전자(甬矽电子)는 AI·HPC·AIoT 쪽에 강점을 가진 패키징·테스트 전문 업체다. 2025년 매출 42~46억위안, 순이익 0.75~1억위안(전년 대비 최대 50.77% 성장)이 예상되며, Bumping+CP+FC+FT 원스톱 라인으로 WLCSP·2.5D·FC-BGA 등 첨단 패키징 비중을 높이고 있다. 캐파 증설과 대형 고객 확대, 규모의 경제가 맞물리며 원가율·비용률이 떨어지는 구조다.

투자·비즈니스 관점에서 기억할 3가지

첫째, 첨단 패키징은 2024년 450억달러→2030년 800억달러로 커지며 가치의 절반 이상을 차지하는 핵심 축이 되었고, 실제 성능·전력·원가 경쟁력의 전장이 이미 공정에서 패키징으로 상당 부분 이동했다.

둘째, Chiplet·2.5D/3D·HBM 확산은 KGD·SLT 등 새로운 테스트 단계와 설비를 ‘강제’로 추가해, 첨단 패키징+테스트 CAPEX를 구조적으로 끌어올린다.

셋째, 중국은 전통 패키징 장비에서 강점이 있고 공정·EDA·장비에서 약점이 큰 만큼, 장전테크·통푸마이크로·화톈테크·융시전자 같은 첨단 패키징/테스트 플랫폼 기업이 AI·HPC 밸류체인에서 레버리지 포인트가 될 가능성이 높다.

'Industry Insight' 카테고리의 다른 글

| [반도체] 자율주행SoC칩 산업 분석 : 시장 잠재력, 경쟁 환경, 밸류 체인 및 관련 기업 (0) | 2026.02.20 |

|---|---|

| [반도체] AI칩 산업 분석 : 성장 동력, 발전 개요, 중국 대체재, 밸류 체인 및 관련 기업 (0) | 2026.02.19 |

| [반도체] 소재 산업 분석 : 발전 현황, 경쟁 구도, 중국 대체재, 시장 잠재력 (0) | 2026.02.17 |

| [반도체] 장비 산업 분석 : 성장 동력, 중국 국내 대체제, 기술 혁신 및 관련 기업 (0) | 2026.02.16 |

| [반도체] EDA 산업 분석 : 주요 동인, 경쟁 환경, 중국 대체재 및 관련 기업 (2) | 2026.02.15 |

댓글